## **UNIVERSIDAD DE VIGO**

Dpto. de Tecnologías de las Comunicaciones ETSI de Telecomunicación

## **TESIS DOCTORAL**

# ESPECIFICACIÓN, VERIFICACIÓN Y MANTENIMIENTO DE REQUISITOS FUNCIONALES CON TÉCNICAS DE DESCRIPCIÓN FORMAL

Autor: Jorge García Duque

Director: Dr. José J. Pazos Arias

## Agradecimientos<sup>1</sup>

Durante el camino recorrido para realizar un trabajo largo y costoso siempre se encuentran obstáculos, momentos en los que uno se siente sólo ante el peligro. Sin embargo, al final del trayecto, cuando se echa la vista atrás, es imposible evitar esbozar esa sonrisa de satisfacción. Los problemas pasados, aquellos momentos de soledad, se ven ahora desde otra perspectiva; y aparecen, casi sin querer, un montón de manos tendidas a lo largo de todo el camino. Y uno piensa, cómo pude encontrar algún inconveniente teniendo tanta gente, tanta ayuda a mi lado. Los problemas surgidos siempre se solventaron gracias a vuestros ánimos, vuestros consejos, vuestra compañía; en fin, gracias a vosotros. Afortunadamente, el final del camino te permite ver que siempre estuvisteis ahí, sin hacer ruido, sin exigir nada. Otra vez tengo que sonreír, recordando los momentos pasados.

Por todo ello, quiero agradecer a cada uno de vosotros todas y cada una de las veces que estuvisteis a mi lado. De tantas maneras distintas. Todas me abrieron las puertas. Cada uno abrió aquéllas que podía abrir. Gracias.

Perdonad si durante el camino no supe valorar vuestro apoyo. Hay veces que sólo es posible ver mirando hacia atrás. Perdonad también si no os pongo nombre, pero vosotros me habéis enseñado que el anonimato de la ayuda desinteresada engrandece aún más el apoyo prestado. Por eso, a todos os tiendo mi mano agradecida, esperando que la recibáis con la misma satisfacción y orgullo con que yo recibí la vuestra. De nuevo, Gracias.

<sup>&</sup>lt;sup>1</sup>Quisiera también agradecer a la Xunta de Galicia el apoyo que nos ha prestado. La financiación recibida a través del proyecto XUGA 32206A97, "LIRA: Contorno software de desenvolvemento de aplicacións con técnicas de descripción formal", nos ha permitido realizar este trabajo con los medios materiales apropiados.

#### Resumen

Esta tesis se enmarca dentro de la *Ingeniería del Software*, disciplina que tiene como objetivo proporcionar teorías, métodos y herramientas para el desarrollo de software de calidad.

La aplicación de las metodologías de desarrollo software tradicionales a sistemas software complejos (sistemas distribuidos) supuso un detrimento en la calidad de los productos software desarrollados, y un incremento en los costes de los mismos; debido, en gran medida, a la imposibilidad de probar el sistema hasta que se disponía de una implementación del mismo.

Las técnicas formales, basadas en la utilización de las matemáticas como vehículo para crear especificaciones de sistemas con una sintaxis y semántica formalmente definida, permiten verificar y validar el sistema en todas las fases del proceso de desarrollo, reduciendo el riesgo de propagar errores a lo largo de dicho proceso. Sin embargo, y a pesar de las ventajas potenciales de los métodos formales, es escasa su integración en la industria del software. Este hecho está motivado principalmente por: el desconocimiento (tanto de clientes como de diseñadores) de estas técnicas; la inexistencia de herramientas apropiadas que permitan su aplicación práctica; así como su deficiente integración en el proceso de desarrollo software. Además, la principal ventaja de estas técnicas (posibilidad de verificar y validar en cualquier fase del proceso de desarrollo) se ve notablemente reducida, debido al alto coste computacional que requiere la verificación formal, cuando se aplican a sistemas de medio y gran tamaño. Una alternativa para solucionar este problema es abordar la verificación mediante refinamientos sucesivos del sistema, siendo la verificación de cada refinamiento mucho más simple.

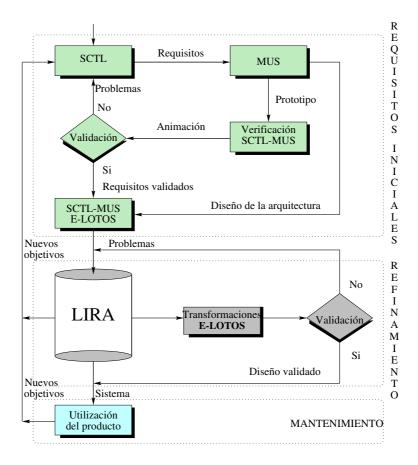

En esta tesis se presenta un modelo de proceso de desarrollo software incremental totalmente formalizado. El trabajo se centra en las primeras etapas del proceso de desarrollo software (especificación, análisis y verificación de requisitos), abordando también la fase de diseño de la arquitectura del sistema y la fase de mantenimiento. El proceso incremental definido permite tratar cada refinamiento del sistema (incremento) de diferente forma, en función de la etapa de desarrollo en que se produzca. Esta idea se basa en dos aspectos fundamentales: por una parte, aprovechar las características complementarias de los distintos tipos de técnicas de descripción formal (orientadas a propiedades para las primeras fases, y constructivas para fases posteriores), combinándolas en función de la etapa de desarrollo; y por otra, adecuar el tratamiento de dichos refinamientos a su naturaleza.

A continuación, se resumen las principales características y aportaciones de la metodología formal desarrollada, clasificándolas según las diferentes etapas del proceso de desarrollo propuesto:

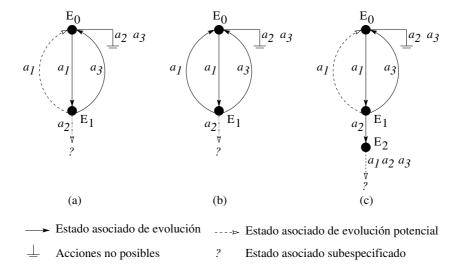

Especificación y análisis de requisitos: Se define una lógica temporal (técnica formal orientada a propiedades) con una semántica cercana al lenguaje natural. La expresividad de dicha lógica se enriquece con la introducción de un tercer grado de especificación denominado subespecificado. Las partes subespecificadas del sistema pueden ser especificadas en refinamientos posteriores del sistema. Además, dada la importancia de establecer con claridad

los requisitos iniciales del sistema, se proporciona una representación gráfica de los mismos a través de un formalismo basado en grafos con arcos en tres estados: posibles, no posibles y subespecificados. Los arcos subespecificados proporcionan grados de libertad y permiten automatizar tomas de decisión en las siguientes fases de desarrollo.

- Verificación: Se proporciona una técnica de verificación basada en model checking, utilizando la lógica temporal definida para la especificación de requisitos y el grafo de representación para realizar la verificación propiamente dicha. Para aumentar la expresividad de las técnicas utilizadas, proporcionando la mayor información posible al usuario, se define una relación de satisfacción con seis grados de verdad; lo que permite expresar el grado de satisfacción de una propiedad y su posible evolución en los refinamientos del sistema.

- Síntesis: A partir de un conjunto de requisitos, se sintetiza automáticamente un grafo de estados según el formalismo definido, proporcionando un prototipo del sistema. El proceso de síntesis se realiza de manera incremental, a medida que el usuario especifica los requisitos del sistema. Dicho proceso automatiza las posibles tomas de decisión, pudiendo sintetizar familias de sistemas que satisfacen el conjunto de requisitos especificados. Además, el proceso de síntesis definido permite reutilizar parte de la síntesis de sistemas con conjuntos de requisitos comunes.

- Diseño de la arquitectura: La definición de requisitos de sincronización y de operadores arquitectónicos permite construir una especificación con estructura del sistema. La elección de los operadores arquitectónicos de E-LOTOS hace que el sistema obtenido (arquitectura inicial del sistema) sirva como entrada en el entorno transformacional LIRA [PA95, GS99], donde puede completarse, en una segunda etapa más orientada hacia la implementación, el proceso de refinamiento.

- Mantenimiento: La definición incremental del proceso de desarrollo permite definir una fase de mantenimiento a nivel de requisitos, ya que la especificación de cada requisito supone un cambio en el sistema, creando versiones del mismo. Cada versión del sistema puede recuperarse a partir de los requisitos que satisface y de las tomas de decisión llevadas a cabo en el proceso de síntesis.

Como complemento al trabajo teórico descrito se ha implementado una herramienta software que integra la totalidad de algoritmos desarrollados. Dicha herramienta incluye una base de datos y una interfaz gráfica que facilita su acceso en un entorno Web.

#### **Abstract**

This PhD. thesis is concerned with the discipline called Software Engineering. The main goal of Software Engineering is to improve the quality of software systems by providing theories, methods and tools for their development.

The quality of software systems was reduced when traditional methods of software development were applied to complex software systems (distributed systems). It was mainly due to the impossibility of proving the system until its implementation was developed, increasing the costs of the product.

Formal techniques, which are based on using mathematics as a vehicle to make system specifications with formally defined syntax and semantics, allow proving and validating systems at all stages of the development process. Therefore, using formal techniques reduces the risk of propagating errors during the software development process. However, in the software industry there is still great reluctance to accept mathematically based software engineering methods. Some of the possible reasons why formal methods have not yet found widespread acceptance in software engineering are: the users' difficulty to understand the formal specifications; the lack of suitable tools (most of which are still prototypes, contain many bugs and are difficult to use); and the deficient integration of formal methods in the software development process. Moreover, the main advantage of these techniques (proving system at all stages of the software development process) is notably limited when they are applied to develop complex systems, due to the high computational load of the formal verification. An alternative to solve this problem is making simple verifications by consecutive refinements of the system. This process ends when the expected product is obtained.

This thesis introduces an incremental model of software development process which is totally formalized. It is focused on the first stages of the software development process (specification, requirements analysis and verification) but it also supports the phases of architectural design and maintenance. The proposed software development model is based on its incremental nature, since the system is successively refined until the final product is obtained. Each refinement is deal with in a different way, according to the development stage. This approach is based on two main aspects: on the one hand, to take advantage of the different kinds of formal description techniques; on the other hand, to deal with the refinements according to their context.

Next, the main features and contributions of the proposed methodology are summarized. They are classified according to the stage of the defined software development process:

• Requirements specification: A temporal logic (a property-oriented formal technique) with semantics close to natural language is defined for specifying system requirements. A new degree of specification is introduced (referred to as *unspecified*) to enrich the expressivity of the logic. Therefore, unspecified parts of system can be specified in subsequent system refinements. Besides, a graphical representation of the logic is provided, due to the relevance of establishing the initial system requirements accurately. To achieve it, a formalism based on graphs with three-valued (possible, non-possible and unspecified) arcs is defined. Unspe-

cified arcs provide different ways to the system evolution and allow automatically carrying out the decision making of the system refinement process.

- Verification: A verification technique based on *model checking* is provided. It uses the defined temporal logic to specify system properties, and the three-valued graphs to make the verification. A satisfaction relation with six degrees of truth is defined. It allows enriching the expressivity of the defined formalisms and providing a detailed verification result, including the current satisfaction degree of the property and its possible evolution during the subsequent system refinements.

- Synthesis: A system prototype is automatically synthesized from the requirements specification by using the formalism based on graphs. The synthesis process is carried out in an incremental way, adding the requirements as the user specifies them. Decision making is automated into this process, being possible synthesizing system families which satisfy the specified requirements. Moreover, the defined synthesis process allows reusing part of systems with subsets of common requirements.

- Architectural Design: System architecture is provided by defining requirements of synchronization and architectural operators. The choice of the E-LOTOS architectural operators makes possible using the obtained system (the initial architecture of the system) as the input of the transformational environment called LIRA [PA95, GS99] in which the system can be refined by specifying E-LOTOS transformations.

- Maintenance: Each specified requirement causes a system refinement. It allows defining

system versions in which the maintenance is made at the requirements specification level.

A system version is identified by a set of requirements and the decision making carried out

during the synthesis process.

A software tool has been implemented as a complement of the theoretical work described above. It integrates all the developed algorithms, including a relational database and a WWW interface.

# Índice General

| Ι | Intr | roducción                                                 | 1  |  |  |  |  |

|---|------|-----------------------------------------------------------|----|--|--|--|--|

| 1 | Áml  | Ámbito y Objetivos de la Tesis                            |    |  |  |  |  |

|   | 1.1  | Introducción                                              | 3  |  |  |  |  |

|   | 1.2  | Ingeniería del Software                                   | 4  |  |  |  |  |

|   | 1.3  | Sistemas Distribuidos                                     | 6  |  |  |  |  |

|   | 1.4  | Los Métodos Formales en el Proceso de Desarrollo Software | 7  |  |  |  |  |

|   |      | 1.4.1 Introducción                                        | 7  |  |  |  |  |

|   |      | 1.4.2 Las Técnicas de Descripción Formal                  | 8  |  |  |  |  |

|   |      | 1.4.3 Verificación Formal                                 | 11 |  |  |  |  |

|   |      | 1.4.4 Los Métodos Formales en la Industria del Software   | 12 |  |  |  |  |

|   | 1.5  | Objetivos de la Tesis                                     | 16 |  |  |  |  |

|   | 1.6  | Organización de la Memoria                                | 19 |  |  |  |  |

| 2 | Esta | do del Arte                                               | 21 |  |  |  |  |

|   | 2.1  | Modelos del Proceso de Desarrollo Software                | 21 |  |  |  |  |

|   | 2.2  | Proceso de Desarrollo con FDTs                            | 25 |  |  |  |  |

|   | 2.3  | Lenguajes de Especificación Formal                        | 27 |  |  |  |  |

|   | 2.4  | Verificación Formal                                       | 32 |  |  |  |  |

|   |      | 2.4.1 Model Checking                                      | 32 |  |  |  |  |

|   |      | 2.4.2 Demostradores de Teoremas                           | 33 |  |  |  |  |

|   | 2.5  | Conclusiones                                              | 34 |  |  |  |  |

|   |      | 2.5.1 Conceptos Fundamentales                             | 34 |  |  |  |  |

|   |      | 2.5.2 Integración de Métodos                              | 35 |  |  |  |  |

|   |      | 2.5.2.1 Model Checking y Demostradores de Teoremas        | 35 |  |  |  |  |

X ÍNDICE GENERAL

|    |      | 2.5.2.2            | Integracion en el Proceso de Desarrollo       | 36 |

|----|------|--------------------|-----------------------------------------------|----|

|    |      | 2.5.2.3            | Educación y Transferencia Tecnológica         | 36 |

| II | De   | finición de la M   | letodología Formal SCTL-MUS                   | 39 |

| 3  | Mod  | lelo de Desarrollo | o Software                                    | 41 |

|    | 3.1  | Combinación de     | FDTs en el Proceso de Desarrollo Software     | 41 |

|    | 3.2  | Modelo de Desa     | rrollo Iterativo con Prototipado              | 42 |

|    | 3.3  | Formalización d    | el Modelo                                     | 44 |

| 4  | Mod  | lelo de Estados S  | ubespecificados: MUS                          | 49 |

|    | 4.1  | Introducción a lo  | os Modelos de Estados                         | 49 |

|    | 4.2  | Definición de M    | US                                            | 51 |

|    | 4.3  | Representación l   | Matricial de MUS                              | 52 |

|    |      | 4.3.1 Introduc     | ción                                          | 52 |

|    |      | 4.3.2 Definicio    | ón de Grafo Subespecificado                   | 52 |

|    |      | 4.3.3 Represen     | ntación Matricial de un Grafo Subespecificado | 53 |

|    |      | 4.3.4 Operacio     | ones sobre Grafos Subespecificados            | 54 |

|    | 4.4  | Ejemplos           |                                               | 55 |

| 5  | Lógi | ica Temporal Ca    | usal Simple: SCTL                             | 59 |

|    | 5.1  | Introducción       |                                               | 59 |

|    | 5.2  | Definición de SO   | CTL                                           | 60 |

|    | 5.3  | Ejemplos           |                                               | 63 |

| 6  | Trac | lucción SCTL-M     | TUS                                           | 65 |

|    | 6.1  | Introducción       |                                               | 65 |

|    | 6.2  | Revisión de la R   | depresentación Matricial de MUS               | 66 |

|    |      | 6.2.1 Operado      | or A La Vez                                   | 66 |

|    |      | 6.2.2 Operado      | or Antes                                      | 68 |

|    |      | 6.2.3 Operado      | or Después                                    | 71 |

|    |      | 6.2.4 Conclus      | iones de la Revisión de MUS                   | 74 |

|    | 6.3  | Traducción de R    | Lequisitos SCTL Atómicos                      | 74 |

ÍNDICE GENERAL xi

|    |                 | 6.3.1    | Algoritmo de Traducción de Requisitos Atómicos I                | 74  |

|----|-----------------|----------|-----------------------------------------------------------------|-----|

|    |                 | 6.3.2    | Evaluación del Algoritmo de Traducción de Requisitos Atómicos I | 76  |

|    |                 | 6.3.3    | Estados de Aplicabilidad de los Requisitos SCTL                 | 77  |

|    |                 |          | 6.3.3.1 Algoritmo de Acciones de Aplicabilidad                  | 77  |

|    |                 |          | 6.3.3.2 Algoritmo de Aplicabilidad Potencial                    | 80  |

|    |                 | 6.3.4    | Algoritmo de Traducción de Requisitos Atómicos II               | 82  |

|    | 6.4             | Algori   | tmo de Traducción SCTL-MUS                                      | 82  |

|    | 6.5             | Traduc   | eción de Requisitos Recursivos                                  | 84  |

|    | 6.6             | Ejemp    | lo del Algoritmo de Traducción SCTL-MUS                         | 85  |

| II | I Vo            | erificac | ión                                                             | 89  |

| 7  | Gra             | dos de S | Satisfacción de los Requisitos SCTL                             | 91  |

|    | 7.1             | Introdu  | acción                                                          | 91  |

|    | 7.2             | Álgebi   | ra de Incertidumbre del Punto Medio                             | 93  |

|    |                 | 7.2.1    | Estructura del Álgebra IPM: Un Álgebra de De Morgan             | 94  |

|    |                 | 7.2.2    | Teoremas Comunes del Álgebra IPM al Álgebra de Boole            | 95  |

|    |                 | 7.2.3    | Reglas y Teoremas sobre Igualdades en un Álgebra IPM            | 96  |

|    | 7.3             | Defini   | ción de la Relación de Satisfacción                             | 97  |

|    |                 | 7.3.1    | Propiedades                                                     | 101 |

|    |                 | 7.3.2    | Orden en el Álgebra IPM                                         | 101 |

| 8  | Veri            | ficación | SCTL-MUS                                                        | 103 |

|    | 8.1             | Introdu  | acción                                                          | 103 |

|    | 8.2             | Interpr  | etación de la Relación de Satisfacción                          | 104 |

|    | 8.3             | Algori   | tmo de Verificación SCTL-MUS                                    | 106 |

|    |                 | 8.3.1    | Descripción                                                     | 107 |

|    |                 | 8.3.2    | Ejemplo de Aplicación                                           | 109 |

| IV | <sup>y</sup> Fa | ase de I | Diseño                                                          | 111 |

| 9  | Sínt            | esis Inc | remental                                                        | 113 |

|    | 9.1             | Introdu  | acción                                                          | 113 |

xii ÍNDICE GENERAL

|    | 9.2   | Descrip  | oción General del Proceso de Síntesis Incremental     | 114 |

|----|-------|----------|-------------------------------------------------------|-----|

|    | 9.3   | Algorit  | tmo de Síntesis: Una Primera Aproximación             | 115 |

|    |       | 9.3.1    | Comparación con el Algoritmo de Traducción            | 115 |

|    |       | 9.3.2    | Reutilización de Estados                              | 117 |

|    |       | 9.3.3    | Pseudocódigo del Algoritmo                            | 119 |

|    |       | 9.3.4    | Ejemplo de Aplicación                                 | 122 |

|    | 9.4   | Conclu   | siones                                                | 125 |

|    |       | 9.4.1    | Pérdida de Subespecificación                          | 125 |

|    |       | 9.4.2    | Valoración del Algoritmo Obtenido                     | 126 |

| 10 | Reut  | ilizació | n en el Proceso de Síntesis Incremental               | 129 |

|    | 10.1  | Algorit  | tmo de Síntesis: En Busca de Reutilización            | 129 |

|    |       | 10.1.1   | Solapamiento de Estados                               | 129 |

|    |       | 10.1.2   | Pseudocódigo del Algoritmo                            | 131 |

|    |       | 10.1.3   | Ejemplo de Aplicación                                 | 131 |

|    | 10.2  | Algorit  | tmo de Síntesis: Aumentando la Reutilización          | 134 |

|    |       | 10.2.1   | Algoritmo de Reducción de Estados                     | 135 |

|    |       | 10.2.2   | Ejemplo de Aplicación                                 | 138 |

|    | 10.3  | Algorit  | tmo de Síntesis: En Busca de Eficiencia               | 139 |

|    | 10.4  | Algorit  | tmo de Síntesis: Independencia de SCTL                | 140 |

|    |       | 10.4.1   | Pseudocódigo del Algoritmo                            | 141 |

|    | 10.5  | Conclu   | siones de los Algoritmos de Síntesis Obtenidos        | 141 |

|    | 10.6  | Algorit  | tmo de Traducción SCTL-MUS: En Busca de Reutilización | 144 |

|    |       | 10.6.1   | Algoritmo de Traducción SCTL-MUS II                   | 146 |

|    | 10.7  | Traduc   | ción MUS E-LOTOS                                      | 147 |

| 11 | Disei | ño de la | Arquitectura                                          | 149 |

|    | 11.1  | Introdu  | ucción                                                | 149 |

|    |       | 11.1.1   | Requisitos de Sincronización                          | 150 |

|    |       | 11.1.2   | Síntesis de un Proceso Sincronizador                  | 151 |

|    | 11.2  | Algorit  | mo de Sincronización                                  | 152 |

|    |       | 11 2 1   | Pseudocódigo                                          | 153 |

| Í | NDICE GENERAL | xiii |

|---|---------------|------|

|   |               |      |

|    |      | 11.2.2   | Ejemplos                                                 | 155 |

|----|------|----------|----------------------------------------------------------|-----|

|    | 11.3 | Proceso  | os Sincronizadores Mínimos                               | 159 |

|    |      | 11.3.1   | Introducción                                             | 159 |

|    |      | 11.3.2   | Síntesis del Sincronizador Mínimo                        | 160 |

|    |      | 11.3.3   | Pseudocódigo                                             | 160 |

|    |      | 11.3.4   | Ejemplo                                                  | 162 |

|    | 11.4 | Reutiliz | zación de Procesos Sincronizadores                       | 163 |

|    |      | 11.4.1   | Ejemplo de Aplicación                                    | 165 |

| V  | Ma   | ntenim   | iento                                                    | 167 |

| 12 | Man  | tenimie  | nto de Especificaciones SCTL-MUS                         | 169 |

|    | 12.1 | Proceso  | os                                                       | 169 |

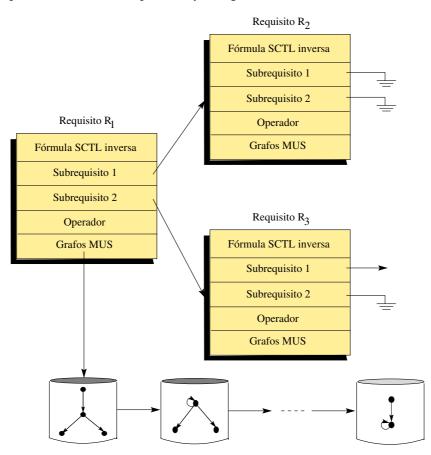

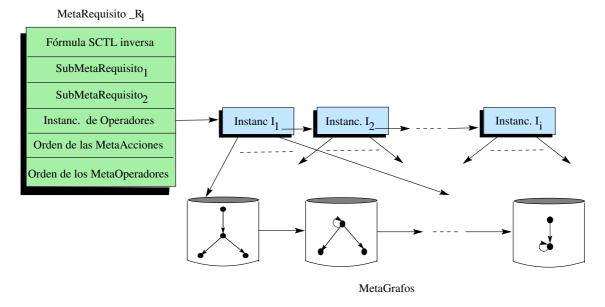

|    | 12.2 | Especif  | icaciones SCTL-MUS                                       | 172 |

|    |      | 12.2.1   | Requisitos SCTL                                          | 173 |

|    |      | 12.2.2   | Grafos MUS                                               | 174 |

|    |      | 12.2.3   | Reutilización                                            | 174 |

| VI | Im   | plemer   | ntación y Ejemplo de Aplicación                          | 177 |

| 13 | Impl | ementa   | ción                                                     | 179 |

|    | 13.1 | Diseño   | Genérico                                                 | 179 |

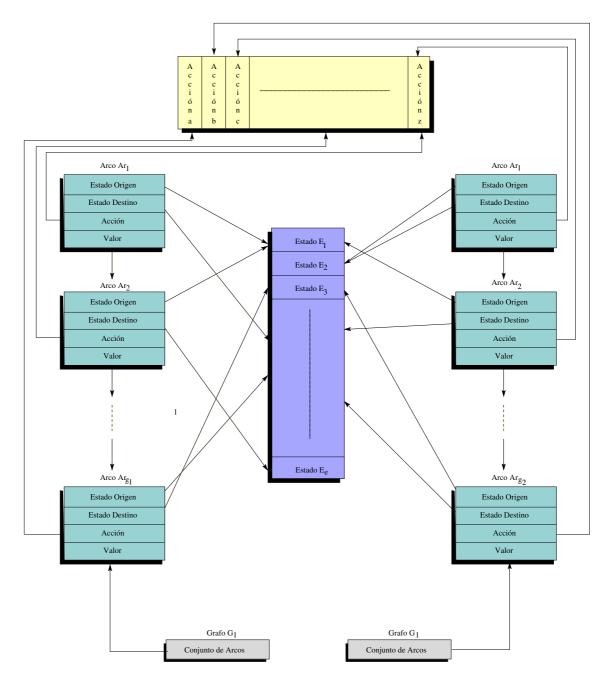

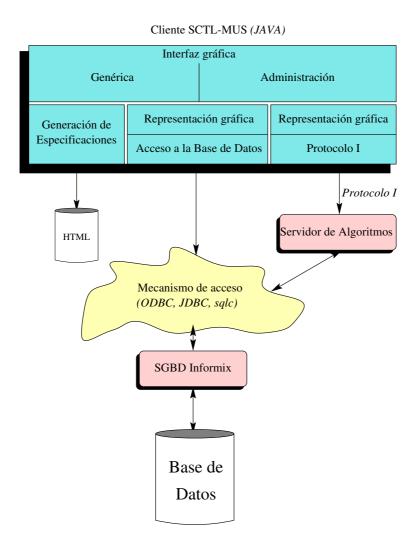

|    | 13.2 | Diseño   | SCTL-MUS                                                 | 181 |

| 14 | Prot | ocolo C  | SMA/CD                                                   | 187 |

|    | 14.1 | CSMA     |                                                          | 187 |

|    |      | 14.1.1   | Descripción                                              | 187 |

|    |      | 14.1.2   | Especificación de Acciones                               | 188 |

|    |      | 14.1.3   | Especificación de los Requisitos de una Estación Emisora | 188 |

|    |      | 14.1.4   | Traducción SCTL-MUS                                      | 189 |

|    |      | 14.1.5   | Síntesis Incremental                                     | 190 |

|    |      |          | 14.1.5.1 Síntesis Parcial                                | 194 |

|    |      | 14.1.6   | Diseño de la Arquitectura                                | 195 |

xiv ÍNDICE GENERAL

|     |       |          | 14.1.6.1    | Proceso Sincronizador $y_1$                        | . 196 |

|-----|-------|----------|-------------|----------------------------------------------------|-------|

|     |       |          | 14.1.6.2    | Proceso Sincronizador $\mathcal{Y}_2$              | . 198 |

|     |       |          | 14.1.6.3    | Proceso Sincronizador Global $\mathcal{Y}_{CSMA}$  | . 198 |

|     |       | 14.1.7   | Verificació | ön                                                 | . 200 |

|     | 14.2  | CSMA     | /CD         |                                                    | . 201 |

|     |       | 14.2.1   | Descripció  | ön                                                 | . 201 |

|     |       | 14.2.2   | Especifica  | ción de Acciones                                   | . 201 |

|     |       | 14.2.3   | Especificae | ción de Requisitos                                 | . 201 |

|     |       | 14.2.4   | Traducción  | n SCTL-MUS                                         | . 202 |

|     |       | 14.2.5   | Síntesis In | cremental                                          | . 202 |

|     |       | 14.2.6   | Diseño de   | la Arquitectura                                    | . 203 |

|     |       | 14.2.7   | Verificació | in                                                 | . 204 |

|     |       |          |             |                                                    |       |

| VII | I C   | onclus   | iones       |                                                    | 209   |

| 15  | Con   | clusione | s y Líneas  | de Trabajo Futuras                                 | 211   |

|     | 15.1  | Conclu   | siones      |                                                    | . 211 |

|     |       | 15.1.1   | Definición  | de SCTL y MUS                                      | . 211 |

|     |       | 15.1.2   | Integración | n en una Metodología Formal de Desarrollo Software | . 213 |

|     |       | 15.1.3   | Algoritmo   | s Desarrollados e Implementación                   | . 214 |

|     | 15.2  | Trabajo  | Futuro .    |                                                    | . 215 |

|     |       |          |             |                                                    |       |

| VI  | II A  | Apéndi   | ces         |                                                    | 219   |

| A   | Ejen  | nplo del | Algoritmo   | de Reducción de Estados                            | 221   |

| В   | Algo  | ritmos   | auxiliares  |                                                    | 225   |

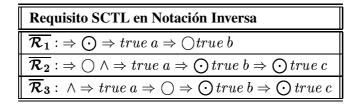

|     | B.1   | Algorit  | mo de Nota  | ación Inversa                                      | . 225 |

|     | B.2   | Algorit  | mo de Card  | linalidad                                          | . 225 |

|     | B.3   | Algorit  | mo de Parti | ción                                               | . 227 |

|     | B.4   | Algorit  | mo de Extra | acción de SubRequisitos                            | . 228 |

|     | Bibli | iografía |             |                                                    | . 228 |

# Índice de Figuras

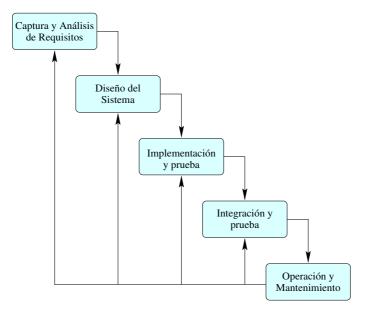

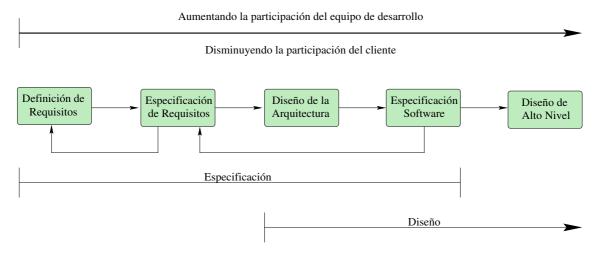

| 2.1 | Modelo en cascada o convencional                                                                   | 22  |

|-----|----------------------------------------------------------------------------------------------------|-----|

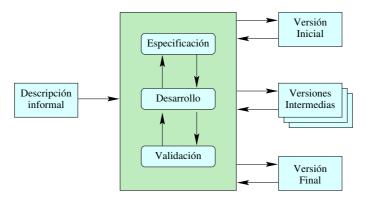

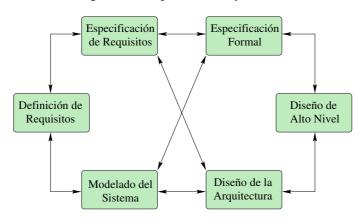

| 2.2 | Modelo evolutivo                                                                                   | 23  |

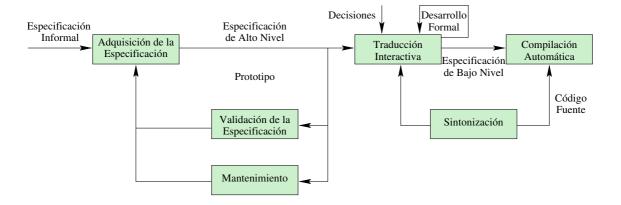

| 2.3 | Modelo transformacional                                                                            | 24  |

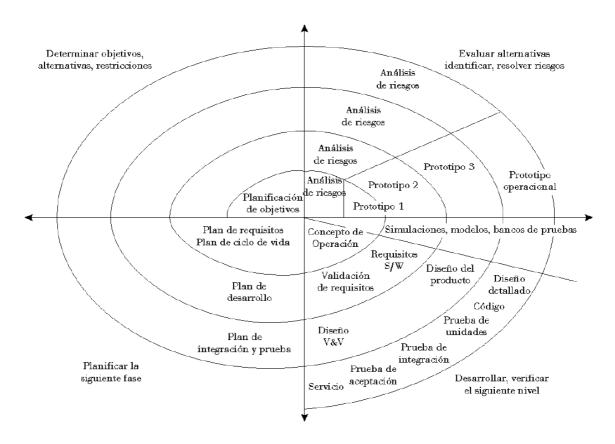

| 2.4 | Modelo en espiral                                                                                  | 25  |

| 2.5 | Especificación y diseño                                                                            | 26  |

| 2.6 | La especificación formal en el proceso software                                                    | 26  |

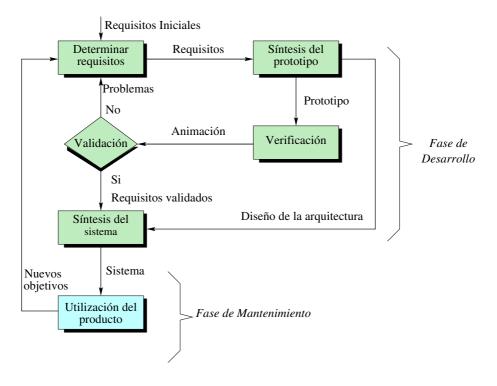

| 3.1 | Ciclo de vida iterativo con prototipado                                                            | 43  |

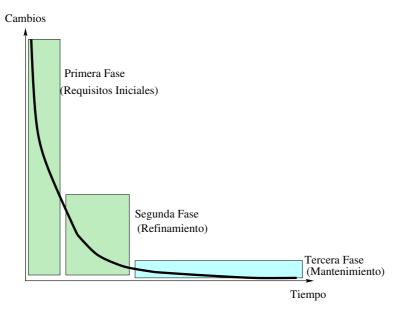

| 3.2 | Evolución de un producto software                                                                  | 44  |

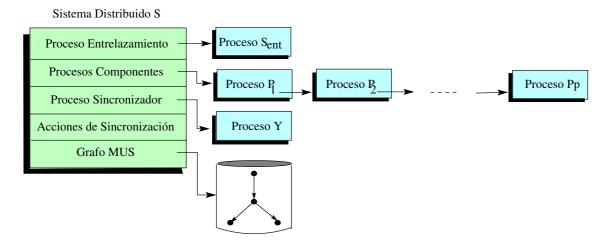

| 3.3 | Modelo de desarrollo software propuesto                                                            | 47  |

| 4.1 | Ejemplo de MUS                                                                                     | 56  |

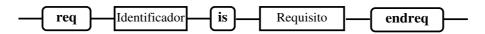

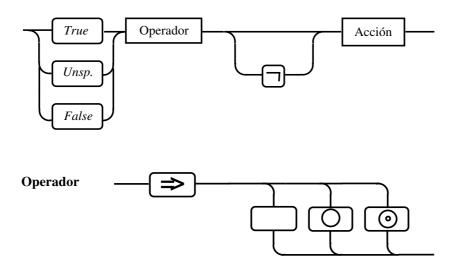

| 5.1 | Sintaxis de la lógica SCTL                                                                         | 62  |

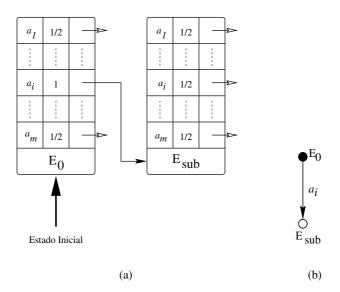

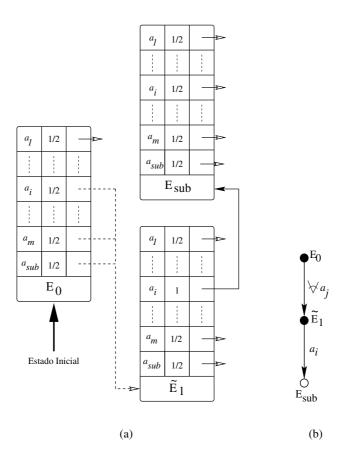

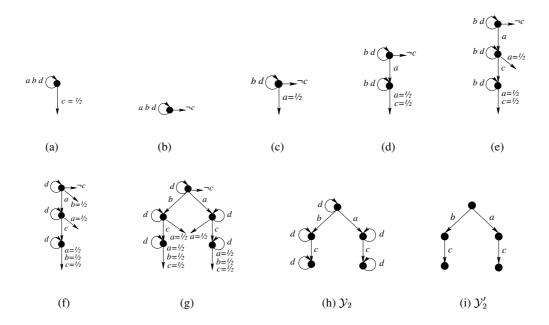

| 6.1 | Grafo MUS del requisito atómico $\mathcal{R}_{at} = true \Rightarrow a_i \ldots \ldots$            | 68  |

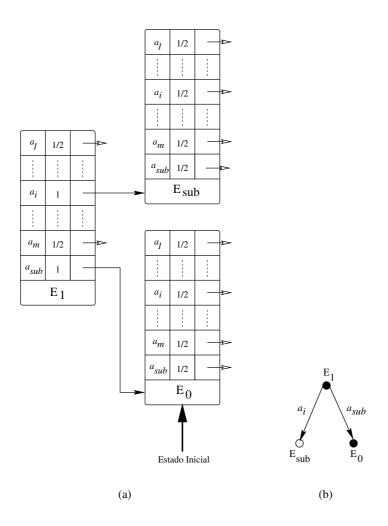

| 6.2 | Grafo MUS del requisito atómico $\mathcal{R}_{at} = true \Rightarrow \bigcirc a_i \ldots \ldots$   | 70  |

| 6.3 | Modelo de estados subespecificados: $true \Rightarrow \bigcirc a_i  \dots  \dots$                  | 71  |

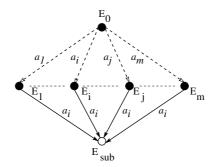

| 6.4 | Grafo MUS del requisito atómico $\mathcal{R}_{at} = true \Rightarrow \bigcirc a_i  \ldots  \ldots$ | 73  |

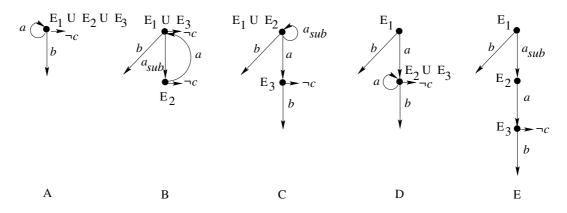

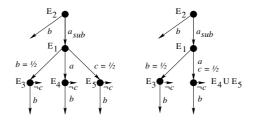

| 6.5 | Traducción del requisito SCTL recursivo $R_{rec}$                                                  | 85  |

| 6.6 | Ejemplo del Algoritmo de Traducción SCTL-MUS                                                       | 85  |

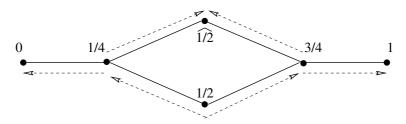

| 7.1 | Álgebra de Incertidumbre del Punto Medio.                                                          | 102 |

| 8.1 | Modelo de estados subespecificados $\mathcal{M}_{grad}$                                            | 104 |

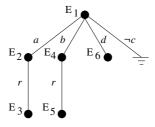

| 8.2 | Grafo MUS del sistema.                                                                             | 109 |

| 0.1 | Grafo MUS del requisito $\mathcal{D}_{\perp} = t_{max} \rightarrow \Omega_{\perp} a$               | 116 |

xvi ÍNDICE DE FIGURAS

| 9.2   | Sistema con infinitos estados                                                                  | 117 |

|-------|------------------------------------------------------------------------------------------------|-----|

| 9.3   | Grafo MUS $\mathcal{M}_{sin}$                                                                  | 118 |

| 9.4   | Pérdidas de subespecificación debidas a la reutilización de estados                            | 118 |

| 9.5   | Grafo MUS $\mathcal{M}_{int}$ de un sistema en una fase intermedia del diseño                  | 122 |

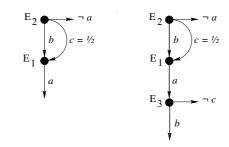

| 9.6   | Síntesis de $\mathcal{R}_1$ . Decisión I                                                       | 123 |

| 9.7   | $\mathcal{R}_2$ no se satisface en $E_2$                                                       | 123 |

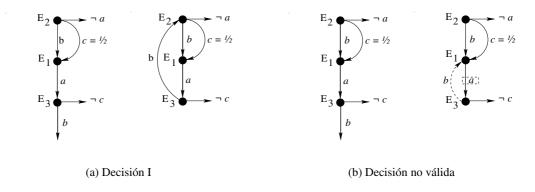

| 9.8   | Síntesis de $\mathcal{R}_1$ . Decisión II                                                      | 123 |

| 9.9   | $\mathcal{R}_2$ no se satisface en $E_1$                                                       | 124 |

| 9.10  | Síntesis de $\mathcal{R}_1$ . Decisión III                                                     | 124 |

| 9.11  | Síntesis de $\mathcal{R}_2$ I                                                                  | 125 |

| 9.12  | Síntesis de $\mathcal{R}_2$ II                                                                 | 125 |

| 10.1  | Grafo MUS del requisito $R_{int}.$                                                             | 130 |

| 10.2  | Unión de dos estados                                                                           | 131 |

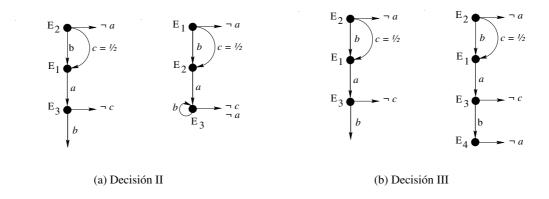

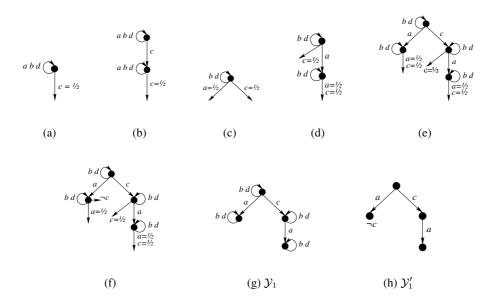

| 10.3  | Grafos MUS del sistema y de los requisitos $\mathcal{R}_1$ y $\mathcal{R}_2$                   | 133 |

| 10.4  | Síntesis de $\mathcal{R}_1$ mediante el Algoritmo 10.1. Decisión I                             | 133 |

| 10.5  | Síntesis de $\mathcal{R}_1$ . Decisión II                                                      | 134 |

| 10.6  | Síntesis de $\mathcal{R}_1$ . Decisión III                                                     | 134 |

| 10.7  | Grafo MUS $\mathcal{M}_1^{\mathcal{R}_{red}}$                                                  | 136 |

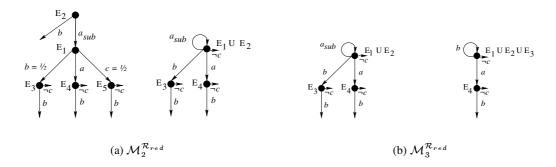

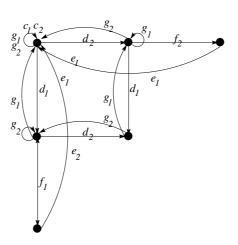

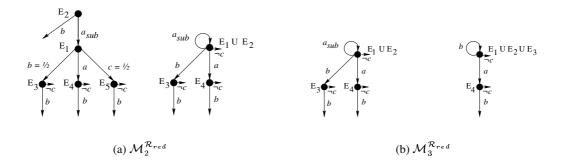

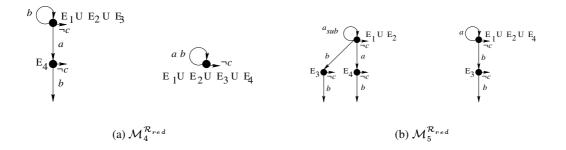

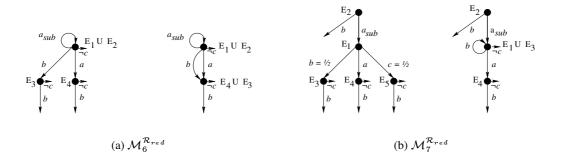

| 10.8  | Grafos MUS $\mathcal{M}_2^{\mathcal{R}_{red}}$ y $\mathcal{M}_3^{\mathcal{R}_{red}}$           | 136 |

| 10.9  | Grafos MUS $\mathcal{M}_4^{\mathcal{R}_{red}}$ y $\mathcal{M}_5^{\mathcal{R}_{red}}$           | 136 |

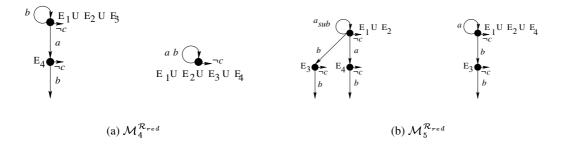

| 10.10 | OGrafos MUS $\mathcal{M}_6^{\mathcal{R}_{red}}$ y $\mathcal{M}_7^{\mathcal{R}_{red}}$          | 137 |

| 10.1  | I Grafo MUS $\mathcal{M}_{int}$ de un sistema en una fase intermedia del diseño                | 138 |

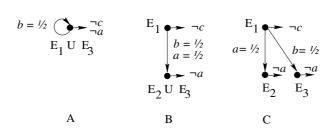

| 10.12 | 2Grafos MUS $\{\mathcal{M}^{\mathcal{R}_2}\}$                                                  | 138 |

| 10.13 | Grafos MUS $\{\mathcal{M}^{\mathcal{R}_1}\}$                                                   | 139 |

| 10.14 | 4Resultado del Algoritmo de Síntesis III                                                       | 139 |

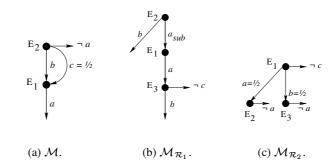

| 10.15 | $5$ Grafo MUS $\mathcal{M}$ de un proceso Tx_Rx                                                | 147 |

| 11.1  | Proceso sincronizador inicial $\mathcal{Y}_{ini}$                                              | 152 |

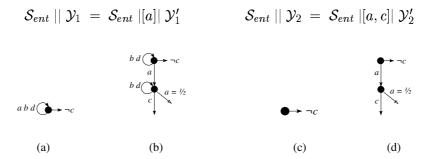

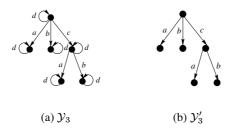

| 11.2  | Procesos sincronizadores $\mathcal{Y}_1, \mathcal{Y}_2, \mathcal{Y}'_1, \mathcal{Y}'_2$        | 153 |

| 11.3  | Grafos MUS de los procesos $\mathcal{P}_1, \mathcal{P}_2, \mathcal{S}_{ent}$ y $\mathcal{S}_1$ | 156 |

| 11.4  | Síntesis del Proceso Sincronizador $\mathcal{Y}.$                                              | 156 |

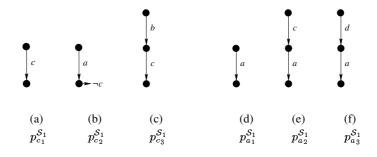

| 11.5  | $\{p_c^{S_1}\}$ y $\{p_a^{S_1}\}$                                                              | 157 |

ÍNDICE DE FIGURAS xvii

| 11.6 Grafo MUS del proceso resultante $S_2$                                                                                                                                         | 158 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 11.7 Síntesis del proceso sincronizador $\mathcal{Y}_2$                                                                                                                             | 158 |

| 11.8 Grafo MUS del proceso resultante $S_3$                                                                                                                                         | 158 |

| 11.9 Síntesis del proceso sincronizador $\mathcal{Y}_3$                                                                                                                             | 159 |

| 11.10Procesos sincronizadores mínimos                                                                                                                                               | 159 |

| 11.11Procesos sincronizadores                                                                                                                                                       | 162 |

| 11.12Síntesis del proceso sincronizador $\mathcal{Y}_{1_{min}}$                                                                                                                     | 163 |

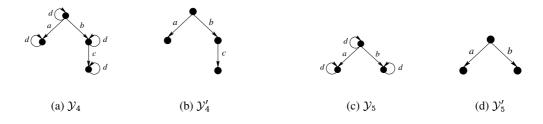

| $11.13\mathcal{Y}_4 = \mathcal{Y}_1 \mid\mid \mathcal{Y}_2, \ \mathcal{Y}_5 = \mathcal{Y}_4 \mid\mid \mathcal{Y}_3. \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 165 |

| 12.1 Mantenimiento de un Sistema Distribuido                                                                                                                                        | 170 |

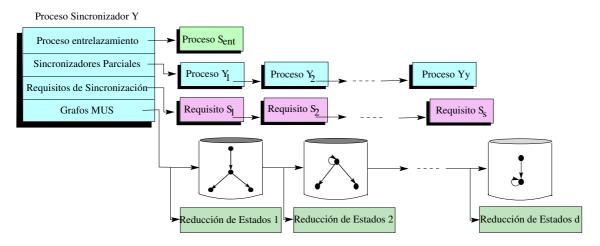

| 12.2 Mantenimiento de Procesos Sincronizadores                                                                                                                                      | 170 |

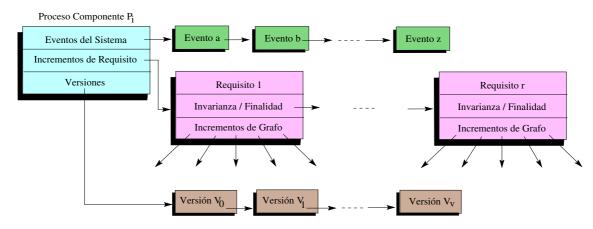

| 12.3 Mantenimiento de Procesos Componentes                                                                                                                                          | 171 |

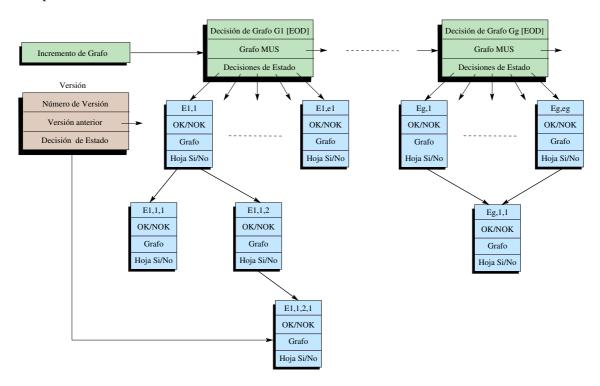

| 12.4 Mantenimiento de Incrementos, Versiones y Decisiones                                                                                                                           | 172 |

| 12.5 Mantenimiento de Requisitos SCTL                                                                                                                                               | 173 |

| 12.6 Mantenimiento de Grafos MUS                                                                                                                                                    | 175 |

| 12.7 Estructura de los MetaRequisitos y MetaGrafos                                                                                                                                  | 176 |

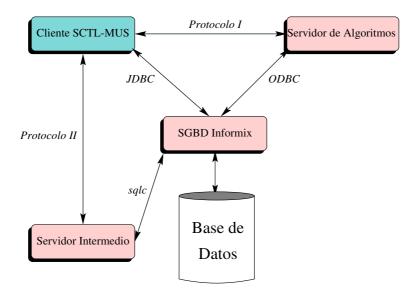

| 13.1 Implementación SCTL-MUS I                                                                                                                                                      | 181 |

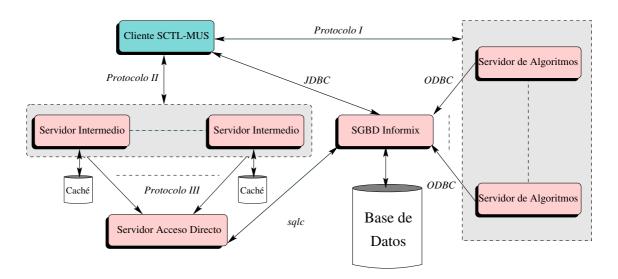

| 13.2 Implementación SCTL-MUS II                                                                                                                                                     | 182 |

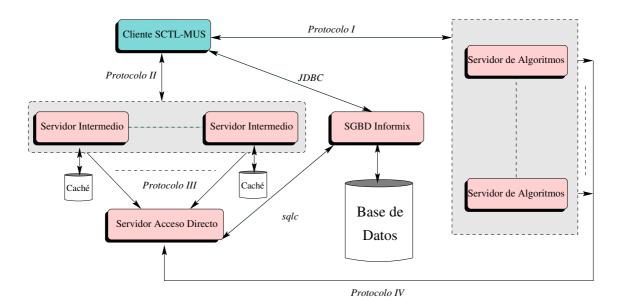

| 13.3 Implementación SCTL-MUS III                                                                                                                                                    | 183 |

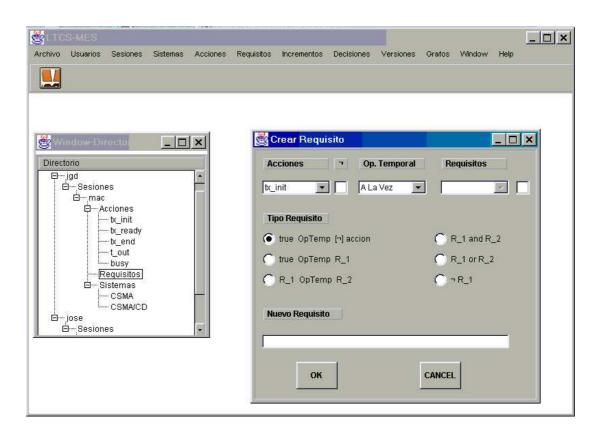

| 13.4 Implementación SCTL-MUS IV                                                                                                                                                     | 184 |

| 13.5 Implementación SCTL-MUS V                                                                                                                                                      | 185 |

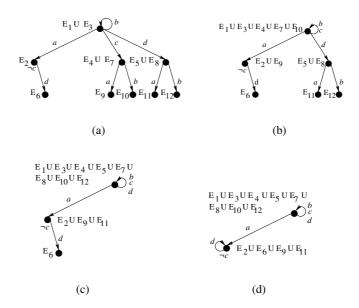

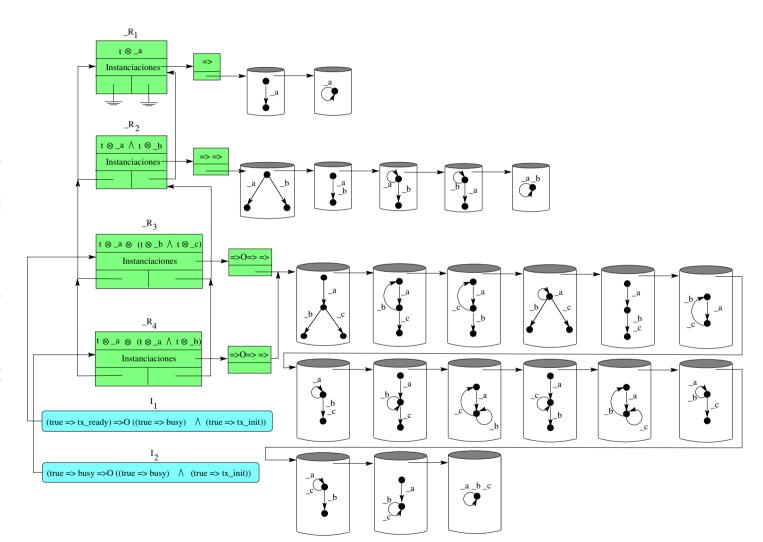

| 14.1 Estructura de MetaRequisitos I                                                                                                                                                 | 191 |

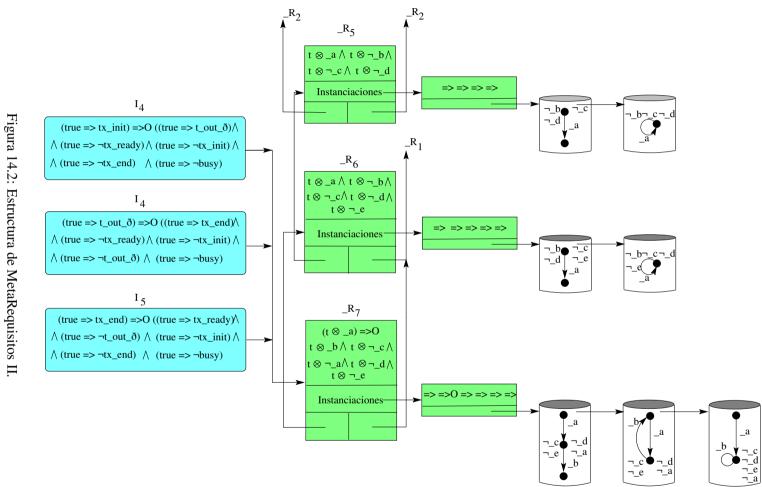

| 14.2 Estructura de MetaRequisitos II                                                                                                                                                | 192 |

| 14.3 Grafo MUS inicial del sistema $\mathcal{M}_{\mathcal{S}}$                                                                                                                      | 193 |

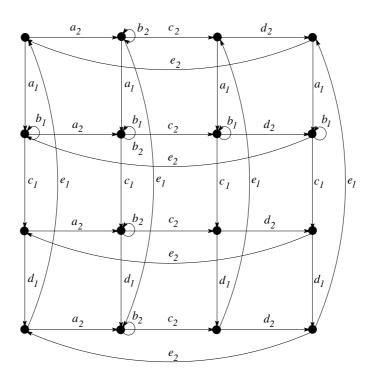

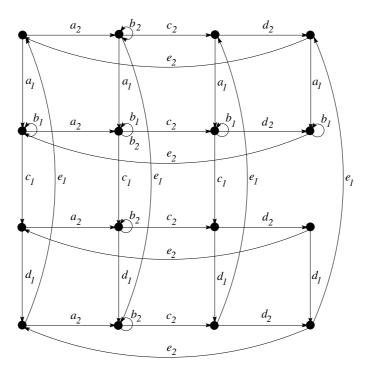

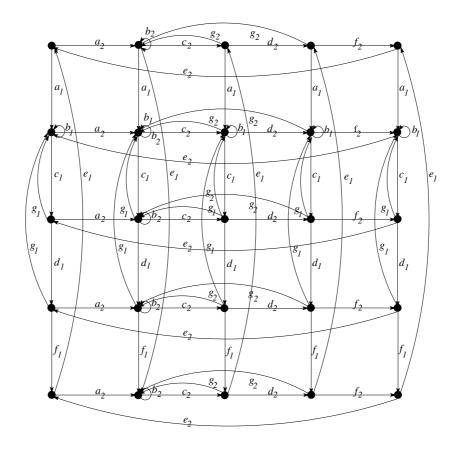

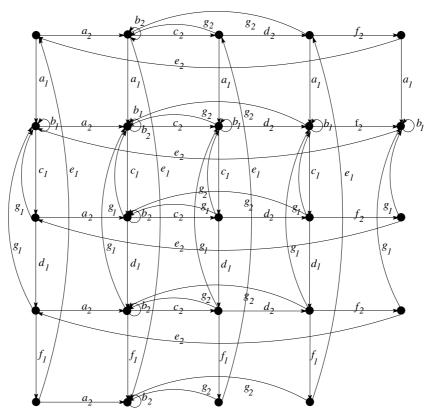

| 14.4 CSMA: Grafos utilizados por el Algoritmo de Síntesis                                                                                                                           | 193 |

| 14.5 CSMA: Grafo final de una estación emisora $\mathcal{E}$                                                                                                                        | 193 |

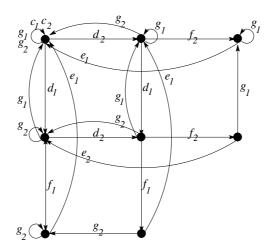

| 14.6 Grafo del proceso entrelazamiento $S_{ent}$                                                                                                                                    | 197 |

| 14.7 Grafo resultante $S_1$                                                                                                                                                         | 197 |

| 14.8 Proceso sincronizador $\mathcal{Y}_1$                                                                                                                                          | 198 |

| 14.9 Grafo resultante $S_2$                                                                                                                                                         | 198 |

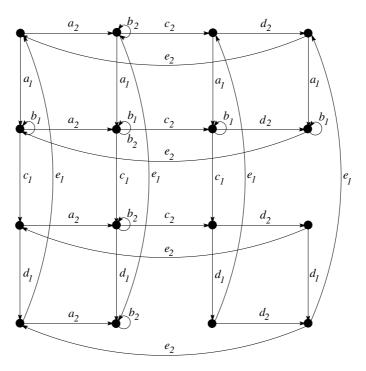

| 14.10Proceso sincronizador $\mathcal{Y}_2$                                                                                                                                          | 199 |

xviii ÍNDICE DE FIGURAS

| 14.11 Grafo resultante $\mathcal{S}_{CSMA}$                                                     | 199 |

|-------------------------------------------------------------------------------------------------|-----|

| 14.12 Proceso sincronizador $\mathcal{Y}_{CSMA}$                                                | 199 |

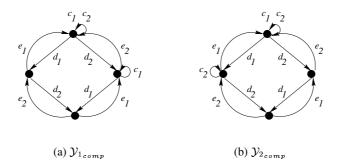

| 14.13 Grafos compatibles de los procesos sincronizadores parciales                              | 200 |

| 14.14 Reutilización del proceso de síntesis                                                     | 203 |

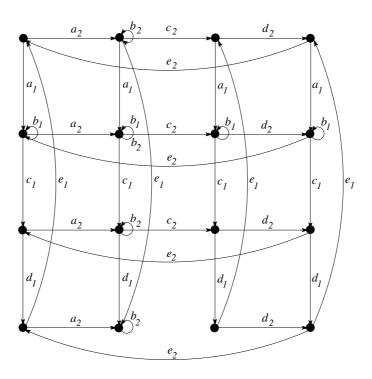

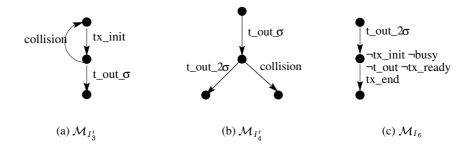

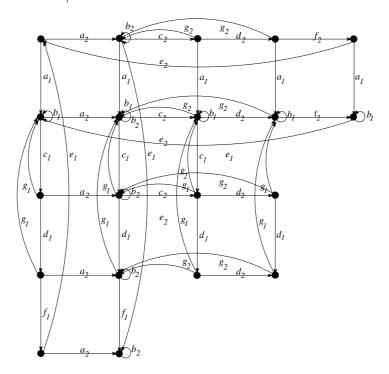

| 14.15CSMA/CD: Grafos utilizados por el algoritmo de síntesis.                                   | 203 |

| 14.16CSMA/CD: Grafo final de una estación emisora $\mathcal{E}'$                                | 203 |

| 14.17 Grafo del proceso entrelazamiento $\mathcal{S}'_{ent}$                                    | 205 |

| 14.18 Grafo resultante $\mathcal{S}_{CSMA/CD}$                                                  | 205 |

| 14.19 Proceso sincronizador $\mathcal{Y}_{CSMA/CD}$                                             | 206 |

| 14.20Grafo resultante $\mathcal{S}'_{CSMA/CD}$                                                  | 207 |

| 14.21 Proceso sincronizador $\mathcal{Y}'_{CSMA/CD}$                                            | 208 |

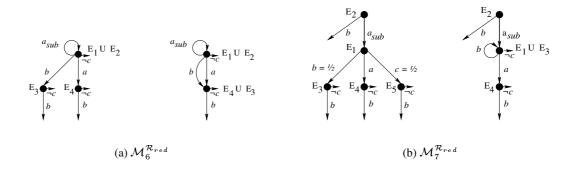

| A. 1. Cuefe MIIS AdReed                                                                         | 221 |

| 1                                                                                               | 221 |

| 2 0                                                                                             | 221 |

| 1 - 0                                                                                           | 222 |

| A.4 Grafos MUS $\mathcal{M}_6^{\mathcal{R}_{red}}$ y $\mathcal{M}_7^{\mathcal{R}_{red}}$        | 222 |

| $T_{ij}$                                                                                        | 222 |

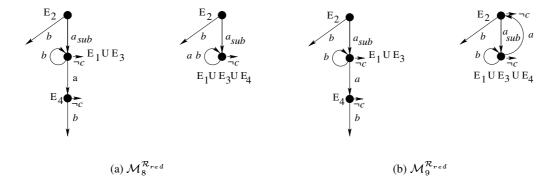

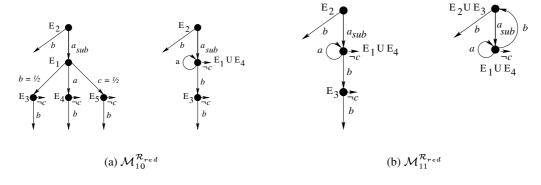

| A.6 Grafos MUS $\mathcal{M}_{10}^{\mathcal{R}_{red}}$ y $\mathcal{M}_{11}^{\mathcal{R}_{red}}$  | 222 |

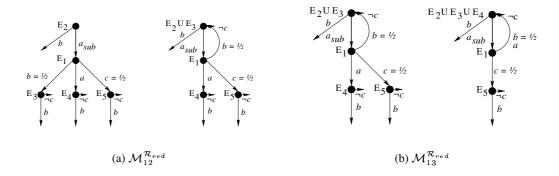

| A.7 Grafos MUS $\mathcal{M}_{12}^{\mathcal{R}_{red}}$ y $\mathcal{M}_{13}^{\mathcal{R}_{red}}$  | 223 |

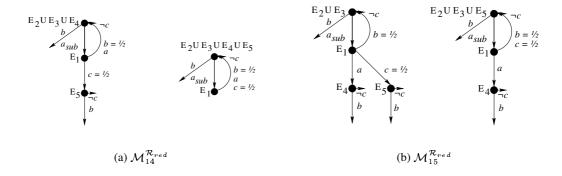

| A.8 Grafos MUS $\mathcal{M}_{14}^{\mathcal{R}_{red}}$ y $\mathcal{M}_{15}^{\mathcal{R}_{red}}$  | 223 |

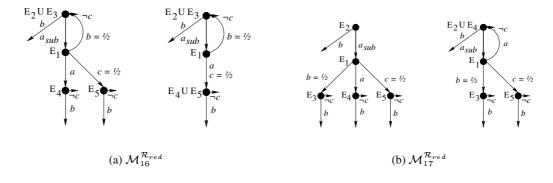

| $\mathcal{D}$ $\mathcal{D}$                                                                     | 223 |

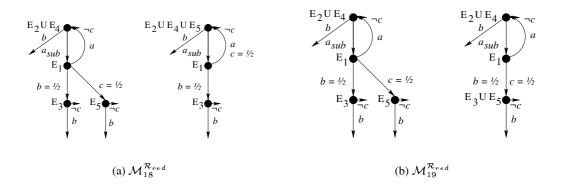

|                                                                                                 | 224 |

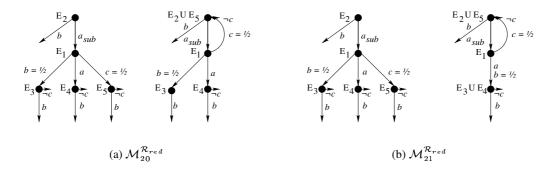

|                                                                                                 | 224 |

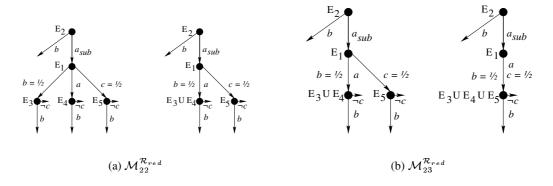

| A.12 Grafos MUS $\mathcal{M}_{22}^{\mathcal{R}_{red}}$ y $\mathcal{M}_{23}^{\mathcal{R}_{red}}$ | 224 |

| A.13 Grafo MUS $\mathcal{M}_{24}^{\mathcal{R}_{red}}$                                           | 224 |

# Índice de Tablas

| 4.1 | Posibles tipos del estado $E_i$ de un grafo subespecificado                                                     | 54 |

|-----|-----------------------------------------------------------------------------------------------------------------|----|

| 6.1 | Representación matricial del requisito atómico $\mathcal{R}_{at} = true \Rightarrow a_i \ldots \ldots$          | 68 |

| 6.2 | Representación matricial del requisito atómico $\mathcal{R}_{at} = true \Rightarrow \bigcirc a_i \ldots \ldots$ | 70 |

| 6.3 | Representación matricial del requisito atómico $\mathcal{R}_{at} = true \Rightarrow \bigcirc a_i \ldots \ldots$ | 73 |

| 6.4 | Grafo MUS inicial $\mathcal{M}$                                                                                 | 75 |

| 7.1 | Leyes no comunes al álgebra de <i>Boole</i>                                                                     | 96 |

| 72  | Grados de satisfacción de un requisito SCTL                                                                     | 98 |

XX ÍNDICE DE TABLAS

# Índice de Algoritmos

| 6.1  | Algoritmo de Traducción de Requisitos Atómicos ( $\overline{\mathcal{R}}_{at} = \bigoplus true[\neg]a_i)$                                    | 76  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.2  | Algoritmo de Acciones de Aplicabilidad ( $\overline{\mathcal{R}}=\{\mathcal{R}[0],,\mathcal{R}[n]\}$ )                                       | 78  |

| 6.3  | Algoritmo de Aplicabilidad ( $\overline{\mathcal{R}}=\{\overline{\mathcal{R}}[0],,\overline{\mathcal{R}}[n]\},E_h)$                          | 79  |

| 6.4  | Algoritmo de Aplicabilidad Potencial ( $\overline{\mathcal{R}}=\{\overline{\mathcal{R}}[0],,\overline{\mathcal{R}}[n]\},E_h$ )               | 81  |

| 6.5  | Algoritmo de Traducción de Requisitos Atómicos II ( $\overline{\mathcal{R}}_{at} = \bigoplus true[\neg]a_i, E_h$ ) .                         | 82  |

| 6.6  | Algoritmo de Traducción SCTL-MUS ( $\overline{\mathcal{R}}=\{\overline{\mathcal{R}}[0],,\overline{\mathcal{R}}[n]\},E_h)$                    | 83  |

| 8.1  | Algoritmo de Verificación $(\overline{\mathcal{R}}, E_h)$                                                                                    | 108 |

| 9.1  | Algoritmo de Síntesis SCTL-MUS $(\overline{\mathcal{R}}, E_h)$                                                                               | 120 |

| 10.1 | Algoritmo de Síntesis SCTL-MUS II $(\overline{\mathcal{R}}, E_h, \{E_h^{\mathcal{R}}\} = \{E_{h_1}^{\mathcal{R}},, E_{h_l}^{\mathcal{R}}\})$ | 132 |

| 10.2 | Algoritmo de Síntesis III $(\{E_h^{\mathcal{M}}\}, \{E_h^{\mathcal{R}}\})$                                                                   | 142 |

| 10.3 | Algoritmo de Traducción SCTL-MUS II ( $\overline{\mathcal{R}}=\{\overline{\mathcal{R}}[0],,\overline{\mathcal{R}}[n]\},E_h$ )                | 146 |

| 11.1 | Algoritmo de Sincronización I $(\mathcal{P}_1,\mathcal{P}_2,\{\mathcal{R}_{\mathit{sinc}}\})$                                                | 154 |

| 11.2 | Algoritmo de Sincronización II $(\mathcal{P}_1, \mathcal{P}_2, \{\mathcal{R}_{sinc}\})$                                                      | 155 |

| 11.3 | Algoritmo de Sincronización III $(\mathcal{P}_1, \mathcal{P}_2, \{\mathcal{R}_{sinc}\})$                                                     | 161 |

| 11.4 | Unir Estados $(\mathcal{Y}, E_1, E_2)$                                                                                                       | 161 |

| B.1  | Algoritmo de Cardinalidad ( $I = \{I[1],, I[n]\}$ )                                                                                          | 226 |

| B.2  | Algoritmo de Partición ( $\overline{\mathcal{R}}=\{\overline{\mathcal{R}}[1],,\overline{\mathcal{R}}[n]\}$ ), $n>3$                          | 227 |

| B.3  | Algoritmo de Extracción Recursivo ( $\overline{\mathcal{R}}=\{\overline{\mathcal{R}}[1],,\overline{\mathcal{R}}[n]\},\ i=1)$                 | 228 |

| B.4  | Algoritmo de Extracción Iterativo ( $\overline{\mathcal{R}} = {\overline{\mathcal{R}}[1],, \overline{\mathcal{R}}[n]}$ )                     | 229 |

# Índice de Ejemplos

| 4.1  | Ejemplo de tipo de estados de un grafo subespecificado     | 57  |

|------|------------------------------------------------------------|-----|

| 4.2  | Representación matricial de MUS                            | 57  |

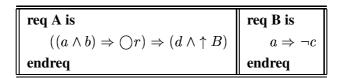

| 5.1  | Ejemplo de requisitos SCTL                                 | 63  |

| 5.2  | Ejemplo de trazas de un requisito SCTL                     | 63  |

| 6.1  | Tipos de especificación soportados por MUS                 | 75  |

| 6.2  | Ejemplo del Algoritmo de Acciones de Aplicabilidad         | 79  |

| 6.3  | Ejemplo del Algoritmo de Traducción I                      | 86  |

| 6.4  | Ejemplo del Algoritmo de Traducción II                     | 87  |

| 7.1  | Ejemplo de requisitos equivalentes                         | 100 |

| 8.1  | Ejemplo de los grados de satisfacción de un requisito SCTL | 106 |

| 8.2  | Ejemplo del Algoritmo de Verificación                      | 110 |

| 10.1 | Ejemplo de Traducción MUS E-LOTOS                          | 148 |

| 11.1 | Ejemplo del Algoritmo de Sincronización II                 | 157 |

| 11.2 | Ejemplo del Algoritmo de Sincronización III                | 162 |

| B.1  | Ejemplo del Algoritmo de Notación Inversa                  | 225 |

| B.2  | Items de un requisito SCTL                                 | 226 |

| B.3  | Ejemplo del Algoritmo de Cardinalidad                      | 227 |

| B.4  | Ejemplo del Algoritmo de Partición                         | 227 |

| B.5  | Ejemplo del Algoritmo de Extracción Recursivo              | 229 |

| B.6  | Ejemplo del Algoritmo de Extracción Iterativo.             | 230 |

# Índice de Definiciones

| 4.1 | Estado de Parada                          | 52 |

|-----|-------------------------------------------|----|

| 4.2 | Grafo                                     | 52 |

| 4.3 | Conjunto de Arcos Tipados                 | 52 |

| 4.4 | Grafo Subespecificado                     | 53 |

| 4.5 | Grafo Subespecificado de Grado $m$        | 53 |

| 4.6 | Matriz de Adyacencia                      | 53 |

| 4.7 | Conjunto de Operadores Temporales Básicos | 55 |

| 5.1 | Fórmula SCTL                              | 60 |

| 5.2 | Requisito SCTL                            | 61 |

| 5.3 | Requisito SCTL Especificado               | 61 |

| 5.4 | Estados de Aplicabilidad                  | 61 |

| 5.5 | Requisito Atómico                         | 61 |

| 5.6 | Trazas de un Requisito                    | 61 |

| 5.7 | Forma Normal Positiva                     | 63 |

| 6.1 | Estado subespecificado                    | 66 |

| 6.2 | Acciones de Aplicabilidad                 | 78 |

| 7.1 | Conjunto de Grados de Satisfacción        | 93 |

| 7.2 | Suma                                      | 93 |

| 7.3 | Producto                                  | 93 |

| 7.4 | Complementación                           | 94 |

| 7.5 | Álgebra de Incertidumbre del Punto Medio  | 94 |

| 7.6 | Álgebra de De Morgan                      | 95 |

| 7.7 | Álgebra de Boole                          | 95 |

| 7 0 | Palación da Satisfacción                  | 08 |

| 7.9  | Satisfacción Atómica          | 98  |

|------|-------------------------------|-----|

| 7.10 | Grado de Satisfacción         | 98  |

| 7.11 | Unión                         | 99  |

| 7.12 | Causal                        | 99  |

| 7.13 | Satisfacción                  | 100 |

| 7.15 | Relación de Equivalencia      | 100 |

| 7.16 | Relación de Orden             | 101 |

| B.1  | Cardinal de un Requisito SCTL | 226 |

| B.2  | Subrequisitos                 | 228 |

## Parte I

## Introducción

## Capítulo 1

## Ámbito y Objetivos de la Tesis

## 1.1 Introducción

La rápida evolución de los ordenadores ha hecho que su aplicación haya sufrido un proceso de continua adaptación durante los últimos 30 años. Inicialmente, las computadoras surgieron como una herramienta de apoyo al cálculo científico, desarrollándose hardware que permitía automatizar dichos cálculos. La aparición del software dotó de una mayor flexibilidad a las computadoras, permitiendo el desarrollo individual de programas o algoritmos que luego se introducían y ejecutaban en las computadoras. El rápido avance en el desarrollo hardware, tanto en el descenso de los costes como en el aumento de la potencia de cálculo de las computadoras, permitió abrir el campo de acción de las mismas, reducido hasta entonces al cálculo matemático.

Se crean, por tanto, nuevas expectativas, lo que conlleva el desarrollo de programas –software–cada vez más complejos. Esta complejidad aumenta con la transformación del ordenador en un nodo de comunicación, lo que permite el desarrollo de nuevos sistemas complejos –sistemas distribuidos– entre los que se encuentran los sistemas software de comunicaciones. Para el desarrollo de estos sistemas software complejos se aplican, inicialmente, los mismos métodos que se aplicaban para el desarrollo de los primeros sistemas software, orientados al cálculo científico. Esto da lugar a una crisis en el proceso de desarrollo de los sistemas software, debido al aumento de los costes y a la baja calidad del software desarrollado; en contraposición con el continuo progreso ya mencionado del hardware, dando origen a lo que se denominó *la crisis del software*.

El problema reside en aplicar métodos conocidos, y desarrollados para otros fines, a las nuevas expectativas que dan origen a los sistemas software complejos. Es necesario, por tanto, un proceso de adaptación, que permita identificar las características de los nuevos productos a desarrollar, así como definir los mecanismos necesarios para reducir los costes y aumentar la calidad de los productos desarrollados. Surge así una nueva área de investigación conocida como *Ingeniería del Software* cuyo objetivo principal es proporcionar teorías, métodos y herramientas para el desarrollo de sistemas software de calidad [NR69].

Son muchos los métodos de desarrollo software estudiados y aplicados en los últimos años,

gracias a los cuales se han logrado grandes progresos en los objetivos planteados —el desarrollo de software de calidad a costes reducidos—; pero lejos de obtener un método o técnica de aplicación general, existe una gran variedad y controversia en los mismos. La comparación con otras ingenierías más asentadas (ingeniería civil, mecánica, etc.) muestra el menor esfuerzo que se dedica en la ingeniería del software al proceso de especificación y análisis de requisitos, así como al proceso de diseño. La razón que explica este hecho, responsable en gran medida de las disfunciones del proceso software, es la escasa formalización de estas fases, lo que imposibilita la realización de tareas de verificación y validación a este nivel. Desde hace años se han dedicado grandes esfuerzos de investigación al empleo de métodos formales en la ingeniería del software. En este ámbito se sitúa el trabajo de esta tesis.

La aplicación práctica de dichos métodos formales en la industria del software encuentra una gran resistencia, debido fundamentalmente a dos deficiencias: la falta de herramientas prácticas que demuestren sus ventajas teóricas; y la necesidad de un nuevo proceso de adaptación en los usuarios y diseñadores, que no están acostumbrados a la utilización de este tipo de técnicas. En cualquier caso, existen argumentos en los dos sentidos, a favor y en contra, y sólo la aplicación real de dichas técnicas dentro de la industria podrá clarificar su situación.

En las siguientes secciones de este capítulo se describen los aspectos más relevantes de la ingeniería del software, definiendo conceptos relativos a la misma. A continuación, se hace una breve introducción a los sistemas distribuidos y a los métodos formales, apuntando sus ventajas e introduciendo la aplicación de las técnicas formales en el proceso de desarrollo de sistemas software. Finalmente, se muestran los objetivos de esta tesis y se hace una breve descripción de la organización de la memoria.

## 1.2 Ingeniería del Software

El objetivo del desarrollo software es crear sistemas que satisfagan las necesidades de los clientes y de los usuarios. Para ello se debe garantizar la calidad del sistema final, lo que hace necesario disponer de un proceso de desarrollo de calidad, definiendo sus actividades y dependencias, así como documentando sus características fundamentales.

Un **proceso de desarrollo software** se define [Som95] como el conjunto de actividades necesarias para el desarrollo de un sistema software. En la actualidad existen varios **modelos del proceso de desarrollo software** que organizan estas actividades de manera diferente, agrupándolas en un conjunto de fases claramente definidas. Cada fase parte de una entrada y produce unos resultados que sirven de entrada a la fase siguiente. El secuenciamiento de dichas fases y los resultados de cada una de ellas varía de un modelo a otro.

Los modelos del proceso de desarrollo software, también denominados **modelos de ciclo de vida**, son en la actualidad uno de los principales campos de investigación dentro de la ingeniería del software. A continuación se describen, brevemente, cada una de las fases identificadas en la mayoría de los modelos de ciclo de vida desarrollados hasta el momento.

• Especificación y análisis de requisitos. En esta fase se establecen los objetivos del sistema, las necesidades de los usuarios o clientes y el dominio de aplicación. Esta fase concluye cuando se dispone de una especificación del sistema software.

En la actualidad, las actividades de esta fase se engloban, dentro de la ingeniería del software, en una disciplina denominada **Ingeniería de Requisitos**, en adelante **RE** (**R**equirements **E**ngineering). En [Std84] se define RE como el proceso de adquisición, refinamiento y consulta de las necesidades de un cliente para el diseño y desarrollo de un sistema software.

En [Std90] se define el término **requisito** como: (a) Una condición o capacidad que un usuario necesita para resolver un problema o alcanzar un objetivo. (b) Una condición o capacidad que debe poseer el sistema para satisfacer un contrato, norma, especificación, u otros documentos formales. (c) Una representación documentada de una condición o capacidad satisfaciendo (a) o (b).

Los requisitos se dividen en **funcionales**, <sup>1</sup> que especifican los servicios que debe proporcionar el sistema; y en **no funcionales**, que especifican las restricciones bajo las cuales deberá operar el sistema (tiempo de respuesta, consumo de recursos, etc.).

• **Diseño**. Tiene como objetivo la determinación de la arquitectura del sistema, descomponiendo el sistema en módulos o componentes. Toma como entrada la especificación del sistema obtenida en la fase anterior, y concluye cuando se dispone de la documentación de cada uno de los módulos, el mecanismo de comunicación entre los componentes del sistema, los algoritmos y las estructuras de datos.

Esta fase suele dividirse en dos partes: en la primera se obtiene un diseño de alto nivel de cada uno de los componentes o módulos del sistema; y en una segunda parte, se refinan dichos módulos hasta obtener un diseño con el nivel de detalle suficiente para pasar a la siguiente fase de implementación.

- Implementación. A partir de la arquitectura software definida se construyen los componentes del sistema, de forma que puedan ejecutarse en el hardware seleccionado.

- Prueba. El objetivo de esta fase es asegurar que el sistema implementado satisface los requisitos especificados (verificación), y las expectativas del cliente (validación). A este proceso se le denomina [Som95] proceso de Verificación y Validación (V&V). En primer lugar, se realizan pruebas unitarias de cada uno de los módulos del sistema. Una vez realizadas las pruebas individuales, se añaden gradualmente cada uno de los módulos del sistema, realizando pruebas de integración.

Existen dos tipos de técnicas aplicables a esta fase: las **técnicas estáticas**, que realizan el análisis sobre representaciones del sistema, tales como la especificación de requisitos, diagramas del diseño o código fuente de los programas; y las **técnicas dinámicas**, que necesitan de una implementación o prototipo sobre el que evaluar el sistema mediante un conjunto de pruebas de ejecución o tests.

<sup>&</sup>lt;sup>1</sup>En este trabajo nos centraremos en los requisitos funcionales.

Según lo expuesto anteriormente, las técnicas estáticas sólo pueden realizar tareas de verificación (comprobaciones con respecto a especificaciones del sistema), mientras que las técnicas dinámicas sí pueden poner de manifiesto que el sistema satisface las expectativas del usuario, a través de tests de comprobación del funcionamiento del mismo.

- Operación y mantenimiento. Una vez que el software ha sido aceptado por el cliente, se

instala y se pone en funcionamiento. A partir de aquí comienza una fase de mantenimiento

en la que se subsanan errores no detectados en fases anteriores y se realizan modificaciones

en el sistema a medida que van surgiendo nuevos requisitos. Existen tres tipos de mantenimiento de software, con características claramente diferenciadas:

- De Corrección: Se centra en la localización de errores. Los de codificación son los más sencillos de corregir; seguidos de los de errores de diseño, ya que conllevan reescribir componentes del programa; mientras que los errores procedentes de la fase de captura y análisis de requisitos son los más costosos, ya que suponen un rediseño del sistema desde su fase inicial.

- De Adaptación: No implica un cambio en la funcionalidad del sistema. Se refiere a

cambios en el entorno del sistema, como el sistema operativo o la plataforma hardware

sobre la que se ha desarrollado.

- De Mejora: Conlleva añadir nuevos requisitos funcionales y/o no funcionales, debido a cambios en las expectativas de los usuarios.

En la actualidad, la fase de mantenimiento constituye un ciclo de vida software completo [Dav93], ya que, si se produce un cambio en los requisitos del sistema, es necesario volver a realizar, total o parcialmente (dependiendo del grado de reutilización que permita el proceso de desarrollo software utilizado) cada una de las fases anteriormente descritas. Esta es la razón por la que esta fase es la más costosa del ciclo de vida, y de ahí la importancia de realizar procesos de desarrollo software que permitan cambios en el sistema con un coste reducido.

### 1.3 Sistemas Distribuidos

El rápido progreso de las aplicaciones de los ordenadores, junto con su cada vez menor precio y mayor potencia de cálculo, ha dado lugar a la aparición de los sistemas distribuidos. Un sistema distribuido se compone de un conjunto de ordenadores autónomos que trabajan de forma coordinada para la realización de una determinada tarea. Estos sistemas suelen estar compuestos por un conjunto de procesos concurrentes que interactúan entre sí. Éste es el entorno típico de las aplicaciones telemáticas, en cuyo ámbito se centra este trabajo.

Una característica común de muchos sistemas distribuidos (protocolos de comunicación, servicios telemáticos, etc.) es que su comportamiento observable no termina nunca, es decir, su

comportamiento se caracteriza más por reaccionar a estímulos del entorno que por terminar produciendo algún tipo de resultado final. Pnueli [Pnu85] denominó **reactivos** a este tipo de sistemas software.

Un sistema reactivo es aquél que no se puede caracterizar adecuadamente mediante una semántica relacional, es decir, mediante una relación entre un conjunto de entradas y sus correspondientes salidas. Es preferible describir este tipo de sistemas a través de la interacción con su entorno. Un sistema reactivo se puede modelar como un generador de trazas, siendo una traza una secuencia finita o infinita de estados o eventos. Cada una de estas trazas puede verse como una secuencia de ejecución. El conjunto total de trazas constituye el comportamiento observable del sistema.

Existen dos posibilidades para expresar el comportamiento observable de un sistema: especificar **explícitamente** el orden de los eventos que pueden suceder en el sistema; o definir las propiedades del sistema, restringiendo **implícitamente** el orden posible de eventos. Una **propiedad** es un conjunto de trazas, siendo una traza una sucesión ordenada de eventos. Un programa satisface una propiedad si todas sus posibles trazas pertenecen al conjunto de trazas de la propiedad.

## 1.4 Los Métodos Formales en el Proceso de Desarrollo Software

### 1.4.1 Introducción

Los modelos tradicionales de ciclo de vida de un sistema software (modelo de ciclo de vida en cascada) muestran numerosas deficiencias cuando se aplican a sistemas complejos. Estas deficiencias son motivadas, en gran medida, por la imposibilidad de realizar pruebas hasta la fase de implementación. Esta problemática se acentúa en los sistemas distribuidos, ya que estos son intrínsecamente más complejos que los sistemas secuenciales clásicos. Esta complejidad se deriva de la necesidad de especificar un conjunto de sistemas secuenciales que deben cooperar y evolucionar en paralelo; siendo la complejidad del sistema final mucho mayor que la suma de las complejidades de los sistemas secuenciales componentes.

Las soluciones a este problema conceden al ordenador un papel más importante en el proceso de diseño y desarrollo de estos sistemas, de forma que el papel del diseñador quede restringido a la toma de decisiones (parte creativa del proceso), dejando al ordenador las tareas de manipulación, análisis y documentación (parte menos creativa).

El uso de una notación formal es decisiva para la solución de los problemas planteados. Por una parte, para capturar en el ordenador toda la información importante de las fases de especificación, diseño, implementación, prueba y mantenimiento, automatizando en la medida de lo posible el proceso de desarrollo software; y por otra, para obtener una especificación precisa, completa y consistente de los requisitos del sistema.

La especificación formal utiliza herramientas matemáticas para construir modelos de sistemas, no ambiguos y susceptibles de verificación. Las matemáticas usadas para la especificación formal

de sistemas son la teoría de conjuntos, la lógica y el álgebra. El objetivo es escribir especificaciones de sistemas con una sola interpretación posible, consistentes y completas.

En otras ingenierías, las matemáticas constituyen una herramienta fundamental de estudio y análisis. Sin embargo, a pesar de las ventajas potenciales que ofrece la aplicación de técnicas formales en la ingeniería del software, están escasamente implantadas a nivel industrial, constituyendo, actualmente, una de las líneas de investigación más importantes dentro de la ingeniería del software. En la sección 1.4.4 se exploran las razones de esta situación.

## 1.4.2 Las Técnicas de Descripción Formal

Es conveniente distinguir entre **métodos formales** y **métodos de especificación formal**. Los primeros se refieren a cualquier técnica, basada en el uso de las matemáticas, aplicable al desarrollo de sistemas software. Los métodos de especificación formal, en los que se centra este trabajo, son métodos formales dedicados a escribir especificaciones de sistemas. La mayor parte de los métodos de especificación formal son notaciones que permiten especificar y razonar sobre el comportamiento de sistemas. Esta característica hace necesaria la experiencia y adecuada formación del equipo de desarrollo para trabajar con abstracciones y modelos de sistemas.

Una **especificación formal** es una expresión matemática que contiene la descripción de un sistema. Una característica deseable, y en algunos casos —en la especificación de normas— necesaria, es que la especificación sea independiente de la implementación; es decir, los detalles de implementación deben incorporarse en fases posteriores.

En la actualidad, existe un amplio consenso en considerar las técnicas de descripción formal, en adelante **FDT**s (**F**ormal **D**escription **T**echniques), como una forma adecuada de describir el comportamiento de sistemas reactivos de procesamiento de la información. Aunque el término FDT se acuñó para denominar los métodos y lenguajes formales normalizados [Tur93], actualmente se utiliza para denominar cualquier técnica o método que permite definir completamente el comportamiento de un sistema (hardware o software) mediante un lenguaje con sintaxis y semántica formales<sup>2</sup>.

Las principales mejoras que se persiguen con el empleo de las FDTs son: corrección del sistema construido respecto a una especificación formal; mejora de la calidad del sistema (entendiendo calidad como el grado de cumplimiento de los requisitos y expectativas planteadas); y aumento de la productividad. En la literatura se pueden encontrar muchos tipos distintos de FDTs.

Las características deseables de una FDT dependen de la fase del proceso de desarrollo en la que ésta se aplique [Bro96]:

- En la fase inicial, de captura y especificación de requisitos, es preferible obtener una especificación flexible del sistema en función de sus propiedades más importantes.

- En la fase de diseño de la arquitectura es necesario poder describir los componentes del

<sup>&</sup>lt;sup>2</sup>A partir de ahora utilizaremos el término FDT con este significado.

sistema, su interfaz y cómo interactúan entre ellos. Es decir, es necesario poder expresar la estructura del sistema especificado.

• En la fase de implementación los componentes tienen que describirse de forma que su comportamiento pueda ser generado por máquinas, y por tanto, es necesario utilizar un lenguaje de programación. El proceso de traducción de un lenguaje de especificación a un lenguaje de implementación se puede automatizar en gran medida [MdM88]. Por tanto, si se emplean FDTs, podemos decir que esta fase es semiautomática.

En la actualidad, no existe homogeneidad en las técnicas de descripción formal sino que existe un amplio conjunto de técnicas. A continuación, se resumen los tipos de técnicas existentes, sus ventajas e inconvenientes.

La clasificación de las FDTs más difundida distingue tres categorías<sup>3</sup>:

1. **Técnicas algebraicas**. Un sistema se modela mediante álgebras *multi-sorted* como un conjunto de tipos y de operaciones sobre esos tipos. Cada tipo (*sort*) tiene un conjunto de valores y un conjunto de operaciones sobre dichos valores.

Las operaciones de un tipo se definen a través de un conjunto de axiomas o ecuaciones que especifican las restricciones que deben satisfacer las operaciones.

Estos métodos son especialmente útiles para especificar interfaces entre los componentes del sistema, considerando en este nivel de abstracción el sistema como un conjunto de tipos abstractos de datos.

Las técnicas algebraicas presentan problemas para la verificación formal de la completitud de las especificaciones.

Ejemplos de métodos de especificación formal algebraicos son: Larch y OBJ.

2. **Técnicas basadas en modelos matemáticos**. Basadas en teoría de conjuntos y lógica de primer orden, las más conocidos son Z, VDM y B.

El espacio de estados del sistema se modela a través de sus componentes que son a su vez modelados mediante conjuntos, funciones, etc. Se pueden formular condiciones invariantes sobre el espacio de estados mediante predicados sobre sus componentes. Las operaciones que manipulan el espacio de estados se especifican mediante predicados que relacionan diferentes estados de los componentes.

La especificación explícita del espacio de estados y de operaciones sobre estados constituye la principal diferencia con las técnicas algebraicas, que no utilizan los estados para modelar un sistema sino tipos abstractos de datos y operaciones sobre tipos.

3. **Técnicas basadas en álgebra de procesos**. Las técnicas citadas anteriormente modelan principalmente propiedades funcionales y comportamiento secuencial. Este hecho limita su aplicación a sistemas secuenciales (sistemas no concurrentes).

<sup>&</sup>lt;sup>3</sup>En el capítulo 2 se detallan las características más significativas de cada una de las técnicas de descripción formal citadas.

Las álgebras de procesos se especializan en modelar las interacciones entre procesos concurrentes. En este tipo de sistemas, propiedades como: seguridad (*el sistema no hace nada malo*) y viveza (*finalmente algo bueno ocurrirá*) son muy importantes.

Estas técnicas son especialmente útiles en la especificación de sistemas distribuidos y concurrentes, como son los protocolos y servicios de telecomunicaciones.

Ejemplos de FDTs basadas en álgebra de procesos son CCS, CSP y LOTOS.

4. **Técnicas basadas en lógica.** Las diferentes versiones de lógica temporal pueden usarse para especificar sistemas.

Estas técnicas permiten especificar explícitamente las propiedades de seguridad y viveza de un sistema. Un sistema se especifica a través de un conjunto de fórmulas de la lógica que definen relaciones y sucesos que ocurren en el tiempo. Permiten trabajar con especificaciones parciales de un sistema.

Estas técnicas son muy apropiadas para la especificación de sistemas de tiempo real.

Su principal inconveniente está en su incapacidad para expresar la estructura –arquitectura–de un sistema, de ahí que se utilicen con más frecuencia en las primeras fases del diseño.

De la clasificación anterior se puede extraer como conclusión que ningún tipo de técnica se adapta perfectamente a todas las fases del diseño y desarrollo de un sistema concreto.

A continuación, se muestra una clasificación de las FDTs en función de los aspectos del sistema que modelan:

- Funcionalidad del sistema (son la mayor parte).

- Propiedades concurrentes. De especial interés para la especificación de sistemas distribuidos y de comunicaciones.

- **Tiempo**. De especial interés para la especificación de sistemas en tiempo real. Están menos desarrolladas que las dos anteriores.

Otra clasificación muy extendida de las FDTs define dos grandes grupos [Got92]:

- Constructivas. Las especificaciones escritas con estas técnicas son ejecutables. Su principal ventaja es su adecuación para realizar un prototipado rápido del sistema final. Su principal inconveniente es la imposibilidad de especificar de forma explícita las propiedades de un sistema, lo que impide la verificación explícita de propiedades. Ejemplos de FDTs constructivas son: LOTOS, CSP, etc.

- No constructivas u orientadas a propiedades. Las propiedades del sistema se expresan de forma explícita. Permiten tratar cada propiedad de forma separada lo que ayuda a decidir si es o no esencial. Su principal inconveniente reside en la dificultad para decidir si la especificación de un sistema es o no completa, es decir, si define únicamente comportamientos

correctos. Este tipo de FDTs son formalismos basados en lógica, como la lógica modal y la lógica temporal.

Por tanto, las técnicas de descripción formal constructivas y no constructivas tienen características complementarias que sugieren combinar su empleo dentro del proceso de desarrollo: FDTs orientadas a propiedades (no constructivas) en la fase inicial de especificación de requisitos y FDTs constructivas en la fase de diseño.

#### 1.4.3 Verificación Formal

Las FDTs proporcionan una marco adecuado para reducir el riesgo inherente a la fase de captura y especificación de requisitos del sistema. No obstante, es importante ser consciente de que una especificación de un sistema escrita en una notación formal puede contener también errores. Para aumentar la confianza del diseñador en la corrección del método es preciso realizar operaciones de verificación sobre la especificación. Muchas veces esta verificación se realiza de manera informal a través de inspecciones y reuniones de revisión. Sin embargo, la base matemática de los métodos de especificación formal posibilita la **verificación formal** en dos aspectos: verificación formal de propiedades formuladas sobre la especificación, y verificación formal de que la implementación satisface la especificación.